In multi-socket systems the actual bus number assigned to it may vary. Note that CPUBUSNO 0 and CPUBUSNO 1 are just symbolic names and are processor relative. By virtue of this, the PCH and the devices connected to it are just a logical extension of the CPU's internal PCI bus 0. The physical DMI2 connection which joins the PCH to the CPU is invisible to configuration software. Since the DMI root port (not complex) and PCIe root port(s) bridge a PCIe layer to a PCI layer they are logically just PCI-to-PCI brides. Collectively this forms the Processor Uncore devices. Similarly, Bus 1 joins the QPI links, interrupt handling, core broadcast, power control, IMC, and performance monitoring to the processor cores. Collectively this forms the Processor IIO Devices. Although the components are now integrated, they are still connected via PCI and are exposed as such to the PC BIOS / UEFI firmware.īus 0 joins the DMI root complex, PCIe root complexes (between one and three depending on the chip), DMA engine, and IIO Core to the processor cores. Intel uses an architecture that they call Integrated IO (IIO) to merge all of the previous platform components into one physical part of the CPU. The PCI devices and PCIe endpoints need not care about the specifics of the system's memory subsystem, endianness, etc.

This allows a PCIe/PCI device to connect to any system that has a compliant root complex / host bridge without regard to the architecture of the rest of the system. The root complex (PCIe) and host bridge (PCI) provide a stateful translation layer between the PCIe/PCI logic on one side, and the system specific logic on the other. The PCIe root complex is to the PCIe architecture as the PCI host bridge is to the PCI architecture. I know there not easy questions to answer but if someone has any information it would be greatly appreciated. Do these lanes then 'use up' some of the lanes from the CPU, for example if I have a 28 PCIe lane CPU, will 8 of those lanes connect to the 8 lanes in the PCH?Īgain, what about the devices internal to the PCH, do these use up any PCIe lanes? My next question is regarding the PCIe lanes originating from the PCH, my Z87 chipset has 8 PCIe lanes from the PCH. They are not behind any Root Ports and are on Bus 0 so would they be part of the Root Complex. If so, what about the devices internal to the PCH (USB Cont., SATA Cont.

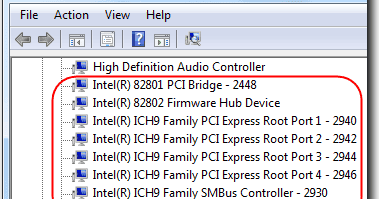

The Root Complex contains Root Ports to connect to the PCIe devices.įirstly, the PCH (southbridge) contains Root Ports and devices that are on bus 0, so is the PCH part of the Root Complex? The 'inner' bus of the root complex is bus 0.

I understand that the PCIe Root Complex is the Host Bridge in the CPU that connects the CPU and memory to the PCIe architecture. I have some questions regrading the PCIe Root Complex, PCIe lanes and the PCH and I am hoping someone here will be able to help as I can't find a clear answer online.

0 kommentar(er)

0 kommentar(er)